Lets take a look at the Core i7 (Jan 2012) –

We’re looking at the pins on the Core i7 processor. We could see that these data bus structures to access the memory banks. There is a reset signal that resets the controller. There is RAS and CAS signal. If you look at these signals, we’re starting to see a pattern. We have 16-address lines , that is 2e16 rows and 2e16 colums , so basically we can have 2e48 bytes of ram , but realistically , it can only support 32GB of RAM. It’s designed to work with that DDR Memory , and it’s control is in built.

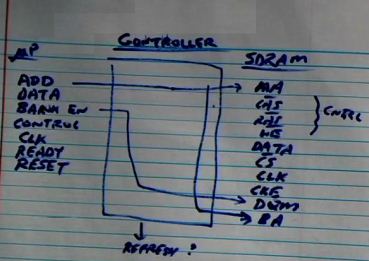

But this is a modern processor. If we must learn how the controller works , we need to build a controller.

The controller that we need must support MT48LC4M16A2 memory device. It also must support a 80386DX or similar processor with 32-bit data bus not having SDRAM support.

I’ll also include state machines , row and column details , bank signal generation , data masking , data flow , ready logic and refresh support. Also inclusive of interfacing with ~ADS , W/~R and M/~IO control signals. Support for AUTO REFRESH commands at a sufficient rate to ensure memory integrity. Attempts to minimize processor waiting due to refresh , Support of the READY logic of the selected microprocessor system , especially when refresh is occurring , unless a bus locking protocol is used. Burst length only limited to 2 transfers although higher burst length may be supported (DMA Operation) if the 2 transfer thing works successfully.

Also , we have lower bit-width memory with higher burst support option. I will use a 16-bit wide memory. We burst length #2 16-bit numbers to get a 32-bit number , which is the width of the data bus. If this one works , I’ll also work on using lower-bit width memories (setting number of registers) and who knows , also variable CL value support.. Why? Cuz they’re cheap.

Lets look at it in a form of a list :

Processor (ADD , DATA , BANK EN , CONTROL , CLK , RESET , READY …)

SDRAM (~CAS , ~RAS , MUX ADD , DATA , ~CS , CLK , CKE , DQM , Bank Address Numbers , A10 bit )

DQM bits tell us about signal bursts and bit-addressing.

In further posts , I will introduce how an SDRAM actually works.