We are going to take a look at the 80386DX processor today.

We need a RESET on the SDRAM controller. Looking at the datasheet , Address Strobe is your signal that says please start the burst cycle and what it is – (IO Read or IO Write). You know the valid address is there , the Bank Enable signals are there and you know whether you are reading or writing.

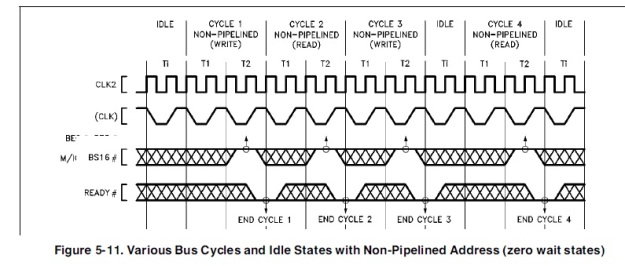

If the processor starts a read-write cycle , but you are in IDLE , you know the data is still there , you still have the address , RD/WR signals – but when you are in a refresh , so anytime when you’re in REFRESH – you make sure READY is not active.

You don’t want garbage values to be read and jank up your system. This makes the processor wait – so that the refresh is over.Every 64ms , you got to do a Refresh – that’s like 6-7 CLKs (@ CLK2 * 2) – for upto 4 of these clocks are are spent in REFRESH. So the waiting period is almost 2 CLK2 Clocks.If you can detect an IDLE peroid , you are garunteed that you will cause no more than 1 wait states and thus saving time.

Reset should go into an initialization state which completes and goes into an idle state.

note – that x is the input to the driver gate. Pay special attention to this.

x = 0 when REFRESH and memory is NOT READY to Write or Read.

Things to do :

We want to wait some period of time to power supply to stable and clocks to stabilize. Wait 100microsec (no. of CLKs based on core clock rate ) , we will need a counter – this allows the memory to come online and system stabilize – (if you start running commands off bat , the memory would seem to work fine but Banks start disabling) .

So basically , wait till 100microsec before transitioning to a new state. Some time in the 100 microsec , bring CKE HIGH – clocking in a command called – COMMAND INHIBIT or NOP. This is done to make sure that commands are being sync’d. Then , PRECHARGE ALL.

Then wait RP time (NOP’s and DESELECT commands must be given) – now all banks are in idle state.

Issue AUTO REFRESH command and then wait RFC time to issue NOP’s.

Then – you’re ready to program mode register. The microprocessor – if it tries to do any reads-writes to memory , we need tot tell it – NOT READY!

Pay attention to how the initialization works. Read this document.

Pay attention to how the initialization works. Read this document.

More insights ahead..